### Junction temperature of CMOS electronics cooled by a regenerative cryocooler

#### **Dmitry Smirnov\***

Thermal Motors LLC, Moscow, Russia

#### Federico Martin Ibanez and Henni Ouerdane

Skolkovo Institute of Science and Technology, Moscow, Russia

#### Abstract

The optimal operation of cryo-CMOS electronics requires an accurate knowledge of the junction temperature, which may be derived from the design parameters of the mechanical cryocooler and cryospace. Research on the subject has been mostly restricted to limited examples of coupled cryocooler-cryocomputer operation with little quantitative analysis. Here, we develop and experimentally validate an analytical relation between the junction temperature and the parameters of the cryospace and cooled to 173 K using a regenerative cryocooler based on the reversed Stirling cycle. The junction temperature was measured in five experiments as a function of five different input clock frequencies. The analytical relation for the junction temperature showed good accuracy with the coefficient of variance of  $\pm 2\%$ , the mean biased error of -2%, and the determination coefficient of 0.92. The result of this work permits determining accurately the steady-state junction temperature of a cryo-CMOS electronics in a wide range of cryogenic temperatures for different types of cryocoolers.

**Keywords:** Cryo-CMOS, regenerative cryocooler, Stirling cryocooler, cryogenic chamber, thermodynamic modelling, cryogenic temperature measurements

\*Corresponding author, <u>dmitry.smirnov@thermalmotors.com</u>, Dmitry Smirnov, ORCID: 0000-0003-4867-9000 Federico Martin Ibanez, ORCID: 0000-0003-1560-4942 Henni Ouerdane, ORCID: 0000-0002-1914-0244

### **I** Introduction

The scaling of silicon transistors below 5 nm to increase computer performance is an arduous task, and it is yet unclear whether this nanoscale technology will entail radically different applications or will merely be used in a conventional fashion. According to Khan *et al.* (2018), "*the semiconductor industry is on the verge of entering uncharted territory for the first time in more than 50 years*", but Kuzmicz (2017) states that silicon-based electronics "*will remain the key technology for logic gates for the next decade or two*". The matter has important implications in the burgeoning sector of quantum computing, and particularly for the application of cryogenic complementary metal–oxide–semiconductor (cryo-CMOS) electronics (Xue *et al.*, 2021). However, fundamental problems still preclude the complete control of qubits-based technologies that would enable the full development of quantum computers (Dyakonov, 2020).

Another approach worth considering is the operation of silicon-based semiconductors or technology under cryogenic temperatures below 77K (Krane *et al.*, 1988; Carlson *et al.*, 1989; Clark *et al.*, 1992; Rose *et al.*, 1999). The empirical findings conclusively showed positive improvements in the operation of CMOS electronics, such as a nine-fold reduction of resistivity, a two-fold or larger increase in clock rate, increased time before first DRAM charge retention failures from several seconds to several hours. The results also suggested the improvement circuit reliability by a factor of  $10^{15}$  against processes activated by higher temperatures, such as diffusion, electromigration, and chemical reactions that follow an Arrhenius law. High-temperature superconductor materials can improve the performance further (Holmes *et al.*, 2013).

Technology feasibility studies of IBM in the early 1990s concluded that no fundamental technical problems existed for cryogenic computing, and the best choice for cooling was the Stirling cycle heat pump. This technology recycles (regenerates) part of the produced cold back

into the process and does not rely on greenhouse refrigerants for its operation (Chu, 1999). However, at that time, the conventional transistor scaling and ambient operation were understandably cheaper than using cryocomputers. The latter implied additional cooling cost, system reliability, and "the need to redesign the technology for optimized low-temperature operation" (Isaac, 2000). The advent of cryo-CMOS electronics as a natural choice for semiconductor-based qubits (Giustino, 2021), physical limits to miniaturize transistors, and a limited number of feasible alternatives for computing technologies (Adamatzky, 2014) motivate to resume experimental work in cryocomputing (Ungerer & Carpenter, 2018, p. 59). The work conducted in the 1980s and 1990s was primarily focused on the fundamental properties of cryo-CMOS electronics using liquid nitrogen. Therefore, the literature is scant with empirical analysis of joint CMOS and cryocooler (cryogen-free) operation and data about designs, materials and performance. The present work provides critical insights into the operation of a joint system "CMOS electronics—cryospace—electricity-based mechanical cryocooler". Here, cryospace, means the space or thermal chamber isolated from the external environment and cooled by a cryocooler. An object of cooling would be located inside this chamber.

This paper aims to find the answer to the question, *what is the fundamental relationship between the junction temperature of the semiconductor electronics and the known and controllable parameters of the cryospace?* Answering this question will help:

- design and control cryospaces using electrical cryocoolers for advanced products in electronics and biomedicine, which require cryogenic temperatures;

- 2) increase the calculation power of computers using traditional CMOS technology;

- design and control the coupled operation of cryospaces and cryo-CMOS electronics for quantum computing.

This work contributes to finding the solution to the research question by developing and experimentally validating an analytical equation between the semiconductor junction temperature and design and operational parameters of the cryospace cooled by a regenerative cryocooler. The article is organized as follows. The following section describes the object of analysis, derives the analytical equation for predicting the junction temperature and discusses the methodology for the validation experiment. Section III shows the experimental results. Section IV discusses the results, limitations and future work. Section V concludes on the findings.

# **II Methodology**

### **II.1** Object of analysis

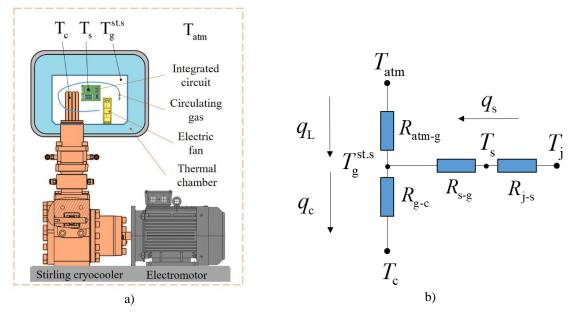

The object of analysis is the thermo-mechanical system "Stirling cryocooler—Thermal chamber—CMOS printed circuit board (PCB)" ("the system"), shown in Fig. 1a. In the figure,  $T_{atm}$  is the atmospheric temperature (K),  $T_c$  is the cryocooler temperature (K),  $T_g^{st.s}$  is the steady-state gas temperature in the thermal chamber ("TC") (K),  $T_s$  is the surface temperature of the heat source, the CMOS integrated circuit (K) ("IC"), and  $T_j$  is the junction temperature of the IC semiconductor (K). An electromotor drives the Stirling cryocooler ("SC"). The latter converts mechanical work into cooling capacity and cools the gas in the TC. The heat transfer is mostly due to forced convection initiated by the gas (air), circulated in the chamber by the electrical fan.

Figure 1b depicts the thermo-electrical analogy of the system. We used this analogy to model thermal balance in the chamber. In Fig. 1b,  $q_c$  is the cooling capacity of the SC (W),  $q_L$  is the sum of all parasite heat leaks from the atmospheric environment (W),  $q_s$  is the heat flow from

Fig. 1. The system "Stirling cryocooler—Thermal chamber—CMOS printed circuit board": a) principal diagram with key elements, b) Thermal-electrical analogy.

| Stirling cryocooler                                  |                                        |  |  |  |

|------------------------------------------------------|----------------------------------------|--|--|--|

| Charge pressure, p                                   | 1.4 MPa                                |  |  |  |

| Shaft frequency, $f$                                 | 9.1 Hz                                 |  |  |  |

| Radiator temperature, $T_{\rm r}$                    | 287 K                                  |  |  |  |

| Design constant, $S_{c}$                             | 90.2                                   |  |  |  |

| Otaka number for given $p$ and $f$ , $\Theta$        | 0.078                                  |  |  |  |

| Working fluid                                        | Helium                                 |  |  |  |

| Width $\times$ height $\times$ depth                 | $262 \times 474 \times 205 \text{ mm}$ |  |  |  |

| Thermal chamber                                      |                                        |  |  |  |

| Circulating gas                                      | Air                                    |  |  |  |

| External width × height ×depth                       | $330 \times 250 \times 425 \text{ mm}$ |  |  |  |

| Internal width × height ×depth                       | 225 × 135 × 275 mm                     |  |  |  |

| External surface area                                | $0.724 m^2$                            |  |  |  |

| Internal surface area                                | $0.259 m^2$                            |  |  |  |

| Heat conductance of the wall                         | $0.040 \ W \cdot m^{-1} \cdot K^{-1}$  |  |  |  |

| Room temperature, $T_{\rm atm}$                      | 297 К                                  |  |  |  |

| Integrated circuit                                   |                                        |  |  |  |

| IC type                                              | CD4049UBE                              |  |  |  |

| Number of ICs on the PCB                             | 3                                      |  |  |  |

| Width × height ×depth                                | $20 \times 5 \times 7 \text{ mm}$      |  |  |  |

| Effective heat transfer area of IC                   | $0.0033 \text{ m}^2$                   |  |  |  |

| Junction-to-case (top) thermal resistance, $R_{j-s}$ | 36.8 $K \cdot W^{-1}$                  |  |  |  |

Table 1. Characteristics of the system's key elements.

an internal source (W) (in this case—an IC),  $R_{atm-g}$  is the total thermal resistance of the system "atmosphere-gas" (K·W<sup>-1</sup>),  $R_{g-R}$  is the thermal resistance of the system "gas-SC" (K·W<sup>-1</sup>),  $R_{s-g}$ is the thermal resistance of the system "heat source-gas" (K·W<sup>-1</sup>), and  $R_{j-s}$  is the thermal resistance of the system "semiconductor juncture-heat source surface" (K·W<sup>-1</sup>). Table 1 lists essential operational, geometrical and thermal parameters of the integrated circuit and the Stirling cryocooler test rig (Smirnov *et al.*, 2019).

#### **II.2** Predicting the junction temperature of the CMOS IC

We first derive an analytical expression for the steady-state temperature of the gas in the chamber as a function of cryocooler control parameters and environment conditions. In a previous work (Smirnov & Ouerdane, 2021), we found and experimentally validated the relation for the steady-state gas temperature in the thermal chamber  $T_g$ :

$$T_{g}^{\text{st.s}} = \frac{R_{g\text{-c}} \cdot T_{\text{atm}}}{R_{\text{atm-g}} + R_{g\text{-c}} - \frac{R_{\text{atm-g}}}{R_{g\text{-c}} \cdot S_{\text{c}} \cdot \Theta \cdot f \cdot p \cdot \frac{1}{T_{\text{r}}} + 1}} = \frac{R_{g\text{-c}} \cdot T_{\text{atm}}}{R_{\text{atm-g}} + R_{g\text{-c}} - \frac{R_{\text{atm-g}}}{R_{g\text{-c}} \cdot C + 1}} = \gamma \cdot T_{\text{atm}}$$

(1)

where the constant  $S_c$  characterizes the Stirling cryocooler design structure (cm<sup>3</sup>),  $\Theta$  is the Otaka number that describes the cryocooler performance (Otaka, 2002), f is the frequency of the cryocooler cycle (Hz), p is the charge pressure (MPa), and  $T_r$  is the temperature of the cryocooler's radiator (K). The frequency and charge pressure were not changed during the experiments; therefore, the value of the cryocooler operational complex C is constant and can be calculated from the values in Table 1. Thermal resistances were constant for the system studied in this work and equal to  $R_{\rm atm-g} = 2.687 \,\mathrm{K}\cdot\mathrm{W}^{-1}$  and  $R_{\rm gc} = 0.771 \,\mathrm{K}\cdot\mathrm{W}^{-1}$  correspondingly. We call the parameter  $\gamma$  in Eq. 1 a *cryospace modifier*, which is equal to 0.563. This parameter will become relevant in the derivations below.

Our objective is to find an analytical relation between the steady-state junction temperature and other *controllable* parameters in the system. Let us first find the expression for the temperature of the gas inside the thermal chamber as a function of heat source and heat sink parameters. Heat sources include heat leaks from the atmosphere  $q_{\rm L}$  and heat generated inside the chamber by the heat source  $q_{\rm s}$  (IC). The heat sink is the heat  $q_{\rm c}$  flowing to the cryocooler. For the steady-state conditions, the relation for the heat conservation reads:

$$q_{\rm c} = q_{\rm L} + q_{\rm s} \tag{2}$$

$$q_{\rm c} = S_{\rm c} \cdot \Theta \cdot f \cdot p \cdot \frac{T_{\rm c}}{T_{\rm r}}$$

<sup>(3)</sup>

$$q_{\rm c} = \frac{T_{\rm g} - T_{\rm c}}{R_{\rm g-c}} \tag{4}$$

$$q_{\rm L} = \frac{T_{\rm atm} - T_{\rm g}}{R_{\rm atm-g}} \,. \tag{5}$$

Equation 3 is the Otaka equation for the cryocooler cooling capacity. Equations 4 and 5 follow from the thermal-electrical circuits analogy. Using equations from 2 to 5, we find the steady-state gas temperature in the chamber as a function of thermal properties, cryocooler parameters, and the heat source power:

$$T_{\rm g} = \frac{R_{\rm g-c} \left(\frac{T_{\rm atm}}{R_{\rm atm-g}} + q_{\rm s}\right)}{1 + \frac{R_{\rm g-c}}{R_{\rm atm-g}} - \frac{1}{R_{\rm g-c} \cdot C + 1}} = q_{\rm s} \cdot \gamma \cdot R_{\rm atm-g} + \gamma \cdot T_{\rm atm} \,. \tag{6}$$

Now, let us derive the relation for the junction temperature  $T_j$ . Heat dissipated from the IC into the environment of the gas chamber can be characterized by two relations:

$$q_{s} = h_{s-g} \cdot A_{s} \cdot \left(T_{s} - T_{g}\right) \tag{7}$$

where  $h_{s-g}$  is the heat transfer coefficient between the heat source wall and the flow of cold gas  $(W \cdot m^{-2} \cdot K^{-1})$  and  $A_s$  is the heat transfer area  $(m^2)$ . The second relation reads:

$$q_{\rm s} = \frac{T_{\rm j} - T_{\rm s}}{R_{\rm j-s}} \tag{8}$$

where  $R_{j,s}$  is the thermal resistance of the IC (K·W<sup>-1</sup>). This value is provided by the IC manufacturer (Table 1). Using equations 6, 7 and 8, the relation for the junction temperature  $T_j$  as a function of controllable parameters of the system reads:

$$T_{j} = q_{s} \left( R_{j-s} + \frac{1}{h_{s-g} \cdot A_{s}} + \frac{R_{g-c} \cdot R_{atm-g}}{R_{atm-g} + R_{g-c} - \frac{R_{atm-g}}{R_{g-c} \cdot C + 1}} \right) + \frac{R_{g-c} \cdot T_{atm}}{R_{atm-g} + R_{g-c} - \frac{R_{atm-g}}{R_{g-c} \cdot C + 1}} .$$

(9)

The estimation of the heat transfer coefficient  $h_{s-g}$  was carried out using the classical empirical relation for the Nusselt number around a hot plate for the characteristic length *L* in the laminar flow with thermal conductivity *k*:

Nu =

$$\frac{h_{s-g}L}{k} = 0.664 \cdot \text{Re}^{\frac{1}{2}} \cdot \text{Pr}^{\frac{1}{3}}$$

. (10)

The gas main flow speed was 1 m·s<sup>-1</sup>, air thermal properties were selected using standard tables for the temperature  $T_g = 173$  K. The characteristic length L was assumed as the wetted contour of the IC parallel to the flow, 17 mm. The effective heat transfer surface was assumed as

one third of the total area of the PCB, where the three ICs were mounted with a fin coefficient of 1.1 to account for the influence of a thermocouple and other electronics and structural elements,  $0.0033 \text{ m}^2$ .

Simplifying the Eq. 9 using  $R_{s-g} = 1/(h_{s-g} \cdot A_s)$  and the notion of the cryocooler modifier  $\gamma$  (Eq. 1), we find:

$$T_{j} = q_{s} \cdot \left(R_{j-s} + R_{s-g} + \gamma \cdot R_{atm-g}\right) + \gamma \cdot T_{atm}$$

(11)

$$\gamma = \frac{R_{\text{g-c}}}{R_{\text{atm-g}} + R_{\text{g-c}} - \frac{R_{\text{atm-g}}}{R_{\text{g-c}} \cdot S_{\text{c}} \cdot \Theta \cdot f \cdot p \cdot \frac{1}{T_{\text{r}}} + 1}}.$$

(12)

Equation 11 shows the relation of the junction temperature to known and controllable parameters of the cryocooler and the cryospace. The summation in brackets represents the total thermal resistance that dissipates the heat generated by the IC in the cryospace with the ambient temperature  $T_g = \gamma T_{atm}$ . Equation 11 can be utilized to control the junction temperature of cryogenic CMOS electronics. Before we move to the experiment, let us analyze the properties of the cryospace modifier.

We first would like to analyze a possible range of values that  $\gamma$  might take and, at the same time, make a preliminary verification of the model results. Four limit cases are noteworthy and described in Table 2 below. Detailed calculations of the limits are in the Appendix. The solution for Case 1 implies that if there is no heat flow between the cryospace and the room, the heat from the IC flows directly to the cryocooler. There is no cooling in Case 2 and 3 because the cryocooler is not working or is effectively isolated. The thermal path goes from the IC to the room environment through the resistances of the thermal chamber. Case 4 is less pronounced than the previous three. It represents the situation of an ideal contact between the cryocooler and the gas in the cryospace.

| Limit<br>case | Case 1<br>Perfect isolation<br>between the cryospace<br>and environment                                       | Case 2<br>The cryocooler is non-<br>functional                                                                    | Case 3<br>The cryocooler is<br>perfectly isolated from<br>the cryospace                                           | Case 4<br>Perfect heat transfer between<br>the cryocooler and the<br>cryospace                                                                                                                                                                                                                                                                        |

|---------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | $R_{\rm atm-g}  ightarrow \infty$                                                                             | $\mathbf{C} = S_{\mathrm{c}} \cdot \Theta \cdot f \cdot p \cdot \frac{1}{T_{\mathrm{r}}} = 0$                     | $R_{\rm g.c} \rightarrow \infty$                                                                                  | $R_{\rm g.c} \rightarrow 0$                                                                                                                                                                                                                                                                                                                           |

| Solu-<br>tion | $\gamma = 0$ $q_{\rm s} = \frac{T_{\rm j} - T_{\rm c}}{\left(R_{\rm j-s} + R_{\rm s-g} + R_{\rm g-c}\right)}$ | $\gamma = 1$ $q_{\rm s} = \frac{T_{\rm j} - T_{\rm atm}}{\left(R_{\rm j.s} + R_{\rm s.g} + R_{\rm g.atm}\right)}$ | $\gamma = 1$ $q_{\rm s} = \frac{T_{\rm j} - T_{\rm atm}}{\left(R_{\rm j.s} + R_{\rm s.g} + R_{\rm g.atm}\right)}$ | $\gamma = \frac{1}{R_{\text{atm-g}} \cdot C + 1} = \frac{R_{\text{c}}}{R_{\text{atm-g}} + R_{\text{c}}}$ $q_{\text{s}} = \frac{T_{\text{j}} - T_{\text{atm}} \cdot \frac{R_{\text{c}}}{R_{\text{atm-g}} + R_{\text{c}}}}{\left(R_{\text{j-s}} + R_{\text{s-g}} + \frac{R_{\text{atm-g}} \cdot R_{\text{c}}}{R_{\text{atm-g}} + R_{\text{c}}}\right)}$ |

Table 2. Analysis of limit cases for the junction temperature equation (Eq. 11)

To understand the meaning of this result, let us first assume that the cryocooler operational complex C ( $W \cdot K^{-1}$ ) represents the heat flow conductance of an additional element in the thermal circuit represented by the cryocooler. The physical meaning of parameter C follows from the cryocooler operational principle. Inside a cryocooler there is an internal temperature  $T_c^{\text{in}} < T_c$ , which is reached using the gas expansion effect. This effect is proportional to the cryocooler gas volume and design  $S_c$ , gas average pressure p, cycle frequency f, temperature of the radiator  $T_r$ , and cooling efficiency  $\Theta$ . Let us call the inverse of C, the cryocooler resistance  $R_c = 1/C$

$(K \cdot W^{-1})$ . Then Case 4 represents a classical solution in electrical circuits for the two-loop circuit. Sources of the two loops for the heat current are the atmosphere and the heat source inside the chamber. In the two-loop circuit, the solution is derived using the Thévenin theorem, whereby the term  $(R_{atm-g} \cdot R_c)/(R_{atm-g} + R_c)$  represents the Thévenin resistance, and the term  $(T_{\text{atm}} \cdot R_{\text{c}})/(R_{\text{atm-g}} + R_{\text{c}})$  is similar to the Thévenin voltage. With this notable result, let us rewrite Eq. 12 utilizing the notion of the cryocooler thermal resistance  $R_{\text{c}}$  for the final form of the cryospace modifier:

$$\gamma = \frac{R_{\rm g-c} + R_{\rm c}}{R_{\rm atm-g} + R_{\rm g-c} + R_{\rm c}}.$$

(13)

Equations 11 and 13 are solution-neutral, which means that different types of cryosystems could be analyzed with these equations. Let us now discuss the methodology to validate the model using the real experiment.

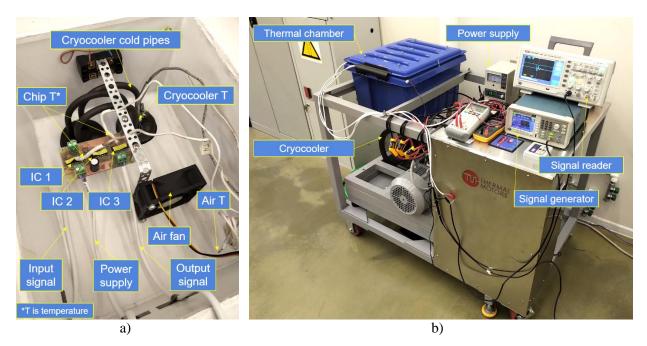

#### II.3 Experimental measurements of the junction steady-state temperature

The increase of IC clock frequency leads to the growth of the junction temperature. This section describes the method that finds the IC junction temperature at each value of clock frequency. Figure 2 depicts an external view of the test setup with the CMOS PCB. The circuit consisted of three ICs (Fig. 2a) for the reliability of measurements. Each IC was a CMOS Hex inverting logic-level buffer and converter CD4049UBE. The ICs were integrated into a whole circuit, which represented a physical model for a simple computational CMOS electronics device. The latter was installed in the thermal chamber (TC) to conduct measurements for three different cooling methods (different from cases discussed in Table 2): 1) cooling by natural convection (Method 1, TC is open), 2) cooling by forced convection with the air fan (Method 2, TC is open), and cooling by forced convection with an air fan and cryocooler (Method 3, TC is closed). The cryocooler test rig is shown in Fig. 2b. The input signal generator, the output signal reader, and the power supply for the circuit were located outside TC.

Four main parameters were controlled during the tests: the IC clock signal frequency,  $f_{\rm IC}$  (MHz), the power supply voltage, U (V), the cryocooler shaft speed, f (rpm), and the cryocooler charge pressure, p (MPa). Only the parameter  $f_{\rm IC}$  was changed during the test. For

Fig. 2. The test setup: a) the internal view of the thermal chamber with the CMOS PCB, b) the external view of the thermal chamber with the cryocooler test rig.

each mode of cooling, the following values of  $f_{IC}$  were used: 1, 5, 10, 15, 20, and 25 MHz. The upper value of  $f_{IC} = 25$  MHz was determined by the frequency limit of available equipment. Power supply voltage was kept at 15 V. Other controlled parameters were kept at constant values according to Table 1.

Four main parameters were measured during tests: circuit current, I (A), temperature of IC surface,  $T_s$  (°C), temperature of circulating gas (air) in the chamber,  $T_g$  (°C), temperature of cryocooler cold pipes,  $T_c$  (°C). Table 2 depicts instrument accuracies according to manufacturers.

It was convenient to use one IC for measurements. We conducted preliminary tests to understand the systematic error caused by imperfections in different manufactured ICs of the same type. For 36 observations of  $T_s$  for IC 1, 2 and 3 at different frequencies, the standard deviation of the measured temperature from the average between IC was  $\pm 2^{\circ}$ C.

Table 3. Instrument accuracy for measured and controlled parameters.

| Measured parameter                                                     | Accuracy     |

|------------------------------------------------------------------------|--------------|

| Circuit current, I, A                                                  | $\pm 0.4\%$  |

| Temperatures, $T_{\rm s}$ , $T_{\rm a}$ , $T_{\rm c}$ , $T_{\rm r}$ °C | $\pm 0.25\%$ |

| Power supply voltage, $U$ , V                                          | $\pm 0.5\%$  |

| Shaft frequency, $f$ , rpm                                             | $\pm 0.05\%$ |

| Charge pressure, $p$ , MPa                                             | $\pm 2.5\%$  |

The main measurements were conducted using one IC for convenience; however, the systematic error of  $\pm 2^{\circ}$ C was used to evaluate the total measurement error of  $T_{s}$ . Average power dissipation  $q_{s}$  over one IC was calculated using Eq. 14:

$$q_{\rm s} = \frac{I \cdot U}{3} \,. \tag{14}$$

# II.4 Evaluation of model accuracy

We selected three metrics to analyze model accuracy: the coefficient of variance, mean biased error, and coefficient of determination. The formulas read:

$$CV = \frac{\sqrt{\frac{1}{n-1}\sum_{i=1}^{n} (x_{i} - \hat{x}_{i})^{2}}}{\overline{x}_{i}} \cdot 100$$

(15)

$$MBE = \frac{1}{n-1} \cdot \frac{\sum_{i=1}^{n} (x_i - \hat{x}_i)}{\overline{x}_i} \cdot 100$$

(16)

$$R^{2} = 1 - \frac{\sum_{i=1}^{n} (x_{i} - \hat{x}_{i})^{2}}{\sum_{i=1}^{n} (x_{i} - \overline{x}_{i})^{2}}$$

(17)

where *n* is the number of experiments,  $x_i$  is the measured value,  $\hat{x}_i$  the predicted value, and  $\bar{x}_i$  the mean measured value. In this work,  $x_i$  takes values of the junction temperature  $T_j$ . For acceptable accuracy, the values of CV and |MBE| should not exceed 5% and be less than 0.95 for  $R^2$ . Smirnov & Ouerdane (2021) discuss these formulas in more detail.

# **III Results**

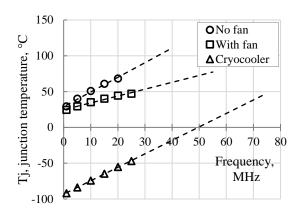

Table 3 aggregates the measurements for three cooling methods, and Fig. 3 visualizes the data graphically and depicts that with the growth of the clock frequency the junction temperature increases.

| Table 3. Results of experiments v | with different methods of cooling |

|-----------------------------------|-----------------------------------|

|-----------------------------------|-----------------------------------|

| $f_{\rm IC}$ , MHz | I, mA                                                                  | U , V           | $q_{\rm s}/3$ , W       | $T_{\rm s}$ , °C | $T_a, ^{\circ}C$ | $T_{j},^{\circ}C$ |

|--------------------|------------------------------------------------------------------------|-----------------|-------------------------|------------------|------------------|-------------------|

|                    |                                                                        | - 7             | Calculated, Eq. 11      | s                | - a '            | Calculated, Eq. 8 |

|                    | Me                                                                     | ethod 1: cooli  | ing the integrated cire | cuit with natu   | ural convectio   | n                 |

| 1                  | 23                                                                     | 15.1            | 0.11                    | 28               | 22               | 32                |

| 5                  | 62                                                                     | 15.1            | 0.31                    | 36               | 22               | 48                |

| 10                 | 104                                                                    | 15.0            | 0.52                    | 45               | 22               | 64                |

| 15                 | 143                                                                    | 15.0            | 0.72                    | 52               | 22               | 78                |

| 20                 | 179                                                                    | 15.1            | 0.90                    | 57               | 22               | 90                |

| 25                 | No data was collected to prevent overheating of the integrated circuit |                 |                         |                  |                  |                   |

|                    | Metho                                                                  | d 2: cooling    | the integrated circuit  | with forced      | convection, ai   | r fan             |

| 1                  | 23                                                                     | 15.1            | 0.11                    | 23               | 22               | 27                |

| 5                  | 62                                                                     | 15.0            | 0.31                    | 26               | 22               | 37                |

| 10                 | 105                                                                    | 15.0            | 0.53                    | 29               | 22               | 48                |

| 15                 | 145                                                                    | 15.0            | 0.73                    | 31               | 22               | 58                |

| 20                 | 180                                                                    | 15.0            | 0.90                    | 33               | 22               | 67                |

| 25                 | 204                                                                    | 15.0            | 1.03                    | 35               | 22               | 72                |

| Ν                  | Aethod 3: coo                                                          | oling the integ | grated circuit with for | ced convect      | ion, air fan an  | d cryocooler      |

| 1                  | 27                                                                     | 15.1            | 0.14                    | -97              | -101             | -92               |

| 5                  | 66                                                                     | 15.1            | 0.33                    | -96              | -101             | -84               |

| 10                 | 107                                                                    | 15.1            | 0.54                    | -94              | -101             | -74               |

| 15                 | 148                                                                    | 15.1            | 0.75                    | -92              | -101             | -65               |

| 20                 | 187                                                                    | 15.1            | 0.94                    | -90              | -101             | -55               |

| 25                 | 216                                                                    | 15.1            | 1.09                    | -87              | -100             | -47               |

Fig. 3. Measured junction temperature from input clock frequency for different methods of cooling

#### **III.1** Model accuracy

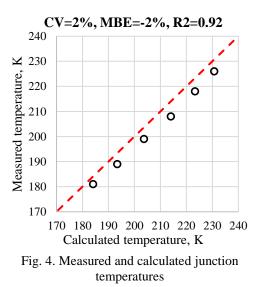

Fig. 4 depicts the comparison of predicted (Eq.11) and measured values of the junction temperature. The coefficient of variance of the model is  $\pm 2\%$ , the mean biased error is -2%, and the coefficient of determination is 0.92. The model predicts with good accuracy when compared with measured values. However, it is also essential to evaluate the accuracy of the measurements. Because there was only one experiment at each IC clock frequency, the estimation of a random measurement error was not possible. However, systematic errors from the instruments and IC property variations were known. The expression for indirect measurements of the junction temperature reads:

$$T_{\rm j} = T_{\rm s} + R_{\rm j.s} \cdot \frac{I \cdot U}{3} \,. \tag{18}$$

From Eq. 18, Table 3, and measured error of different IC  $\sigma_{IC}$ , the systematic measurement error for  $T_j$  is  $\sigma_{T_j} = \sqrt{\sigma_{IC}^2 + \sigma_{T_s}^2 + \sigma_U^2 + \sigma_U^2}$ . It follows that the total systematic error caused by the variation of IC properties, ammeter, voltmeter, and thermocouple is  $\pm 2.1\%$ . The error for the model-predicted value is  $\pm 2\%$ , which puts the prediction *within the observational error range*. From Fig. 4, it is evident that the model systematically predicts higher values with the mean biased error of -2%. Possible sources of this systematic error include inaccuracies in calculating resistances and the cryospace modifier in Eq. 12.

#### **IV Discussion**

It can be inferred from Fig. 3 that for the selected junction temperature  $T_j = 50^{\circ}$ C, the computational performance of a CMOS IC operated inside the cryospace has an improvement performance potential with the factor of 3 compared with simple fan cooling. This result does not come as a surprise. Previous experimental studies, albeit limited, demonstrated similar improvements of the computational frequency with the factor that ranged between 1.5 and 2.3, depending on the study (Chu, 1999; Clark *et al.*, 1992; Carlson et *al.*, 1989). However, little was known about the exact operating conditions and design parameters of the system. This study fills this crucial gap by deriving and experimentally validating an analytical relation (Eq. 19) between the junction temperature and cryospace operational and design parameters. This formula would be helpful to analyze cryo-CMOS electronics of a wide range of designs parameters and cooling temperatures, provided that the thermal resistances are estimated accurately.

$$T_{\rm j} = q_{\rm s} \cdot \left( R_{\rm j-s} + R_{\rm s-g} + \frac{R_{\rm g-c} + R_{\rm c}}{R_{\rm atm-g} + R_{\rm g-c} + R_{\rm c}} \cdot R_{\rm atm-g} \right) + \frac{R_{\rm g-c} + R_{\rm c}}{R_{\rm atm-g} + R_{\rm g-c} + R_{\rm c}} \cdot T_{\rm atm} \,. \tag{19}$$

Previously (Smirnov & Ouerdane, 2021), we discussed the urgent need to better describe the cryospace operation as a function of an electricity-based cryocooler's known design and operation parameters. This conceptualization is most important as more advanced products and technologies need cryogenic temperatures for the operation. The computational performance potential demonstrated a notable improvement just by cooling the integrated circuit to a very low temperature. With more research on computing using superconductive materials, cryocomputing could demonstrate even better performance. Therefore, the development of relation for temperatures inside the cryospace for internal heating sources is essential for analytical and design purposes. Equation 6 describes a validated analytical relation for the cryospace gas temperature and internal heat sources, and Equation 19 characterizes the core temperature of the heat source operated in the cryospace. Experiment measurements demonstrated that the coefficient of variance ( $\pm 2\%$ ), mean biased error (-2%) and the coefficient of determination (0.92) of predictions are at an acceptable accuracy level. We additionally calculated the systematic observational error in the experiment ( $\pm 2.1\%$ ). The prediction error of the model ( $\pm 2\%$ ) is within the range of the measurement error. We implied from these results that our model makes predictions accurately enough within the uncertainty of the experimental validation. These formulas will be helpful to advance the field in the future.

The cryocooler creates an organized sink of dissipated heat to the external environment through the cryocooler. Dissipated heat produced during the computation could be pumped to a particular system for heat recovery. This approach evokes a closer look at the coupling of the cryospace with a heating source and the external environment. In this work, the amount of dissipated heat in the cryospace was negligible (Table 3). More significant amounts of heat can be dissipated using two basic approaches. The same IC can be operated at higher clock frequencies. Alternatively, more ICs can be located in the cryospace. Tradeoffs between these approaches would depend on the functionality expected from the cryocomputer and the limitations of the heat transfer from ICs.

Coupling the cryocooler to the system for heat recovery is another interesting problem. In principle, this approach can recover most of cryocooler's energy input and the pumped heat from

the cryospace (Smirnov, 2021). However, the heat recovery technology has a minimum input temperature, which is higher than a typical temperature of the cryocooler's heat sink. For example, absorption chillers for space cooling need a minimum temperature of around 350 K to operate (Amiri *et al.*, 2021), and the cryocooler in this work had the heat sink temperature of 293 K. This means that the operational and design parameters of the cryocooler would need to be changed to accommodate a hotter heat sink requirements. On the other hand, the change of boundary conditions would also affect the cryospace temperatures. Coupling effects change the entire thermal state of the system. The effect of changing boundary conditions on cooling devices was studied previously by Apertet *et al.* (2018), and future work could explore the effects of coupling using expressions 6 and 19.

#### **IV.1** Limitations

Because of equipment limitations, we were unable to measure the temperature of the IC at clock frequencies  $f_{IC}$  exceeding 25 MHz. Although the dependence is linear in the range between 0 and 25 MHz (Fig. 3), a different relation is possible at higher frequencies.

Another limitation is that we carried out only one experiment for each IC frequency. We partially addressed this limitation by measuring temperature differences between three identical ICs for the same operational conditions. The standard deviation of temperatures was  $\pm 2\%$ . However, more experiments would help to account for the influence of other random factors. They include different room conditions, changing temperature of the cooling water, variation of frequency in the electrical grid that powered the electromotor, changing operation of the air fan in the cryospace, or changing thermal properties of materials under cryogenic conditions. From our experience of operating the cryocooler within the range between 108 K and 200 K, these

differences would not influence the result significantly. However, the operation at cryogenic temperatures lower than that range would result in the presence of random factors, which are unique for ultra-low temperatures.

Our model calculates the heat transfer coefficient using an empirical relation of the Nusselt number for the laminar flow around the plate (Eq. 10). The IC in our experiment (Fig. 2a) can be characterized as a plate but with some reservations. Measuring the exact heat transfer surface area of the IC was problematic. As a heat source, the IC is not isolated from the circuit board, which does not produce any heat. However, some heat flows to the board through the thermal conduction because of the connection between the IC and the board and dissipates in chamber environment through the thermal convection. As a result, the effective heat transfer surface is not isothermal and has a temperature gradient, with the IC having the highest temperature. The thermocouple, which measured the surface temperature, directly contacted the IC, thus increasing the effective heat transfer area. In addition, it created local vortices that changed the heat transfer conditions near the IC. Moreover, the surface of the IC and the printed circuit board included structural elements that increased the effective surface area. It was challenging to measure these surface variations accurately. The effective surface area of the heat exchange, in this case, was larger than the wetted surface area of the IC. Therefore, we used one-third of the total printed circuit board surface area with a coefficient of 1.1 to account for additional elements on the surface of the circuit. We later validated this assumption using experimental data by calculating the product of  $h_{s-g} \cdot A_s$ (Eq. 7), 11.87 W  $\cdot$  K<sup>-1</sup>, and comparing it to the model calculation, 10.12 W  $\cdot$  K<sup>-1</sup>. Future studies should pay more attention to selecting the empirical relation for the Nusselt number and estimation methods for the heat transfer coefficient from the IC.

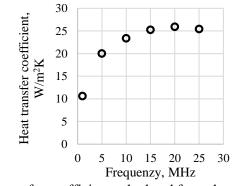

Another assumption is the constancy of the heat transfer coefficient near the wall of the IC where the temperature  $T_s$  was measured. This assumption was introduced to develop a tractable hence physically transparent model. Thermal properties of air were used for the temperature of 173 K. However, in reality, the heat transfer coefficient changed with increased input signal frequency and temperature of the surface (Fig. 5).

Fig. 5. Heat transfer coefficient calculated from the measurements

Equation 9 provides a great deal of explanation of how operational and design parameters of the system influence the junction temperature  $T_j$ ; however, the formula says nothing about the design parameters of the IC. One would need to optimize electronics to work at cryogenic temperatures (Isaak, 2000; Chu, 1999). A dedicated study of the relation between cryogenic temperatures and architectural, structural, material and operational design decisions of the cryo-CMOS electronics would offer valuable insights and would help to design optimal cryocomputers and electronics. Some experimental and conceptual works related to cryo-CMOS electronics have been published recently (Xue *et al.*, 2021; Pauka *et al.*, 2021). Nevertheless, they primarily focused on the electronics design but not on the coupled design and operation of electronics and cryospace.

The energy to run a cryocooler is several times larger than the energy consumption of advanced computer processors. For example, the cryocooler power consumption in this study to

cool a space with a shoebox-size to 173 K was 850 W. At the same time, the heat dissipation of a commercial computer processors is around 200 W. In other words, to increase the computational performance with the factor of 3-assuming that the processor is optimized for low temperatures—one needs to use an extra 850 W of energy just to cool a processor to cryogenic temperatures. However, when the frequency would be actually increased, the power dissipation would also increase, effectively heating the cooling gas in the cryospace. In order to pump more heat out of the cryospace and keep the temperature of the gas at a set constant level, the cryocooler would need additional energy from the grid. Extra energy cost might not be justified because the efforts to reduce watts needed per million instructions per second using conventional approaches were successful in the past (Roser and Ritchie, 2013) and finding novel approaches (such as cryocooling) might not be urgent. And yet, jamming more transistors on the circuit becomes an increasingly challenging task, and the increase of computational performance through this approach might not have substantial grounds any longer. Perhaps, another way to put the question of extra energy cost is to ask, how to make computers faster and waste less energy? We discussed above that a joint operation of the cryocomputers with a heat recovery system for space cooling or other applications might be an exciting avenue for future research. In addition to future trends and the possibility for heat recovery that might justify extra energy cost to run a cryocooler, there are several advantages of cryo-CMOS device discussed in the introductory section. Could the increased energy cost be offset by the benefits of a substantial decrease of the electrical resistivity, increased DRAM storage time by several orders of magnitude, and improved device and circuit reliability (Clark et al., 1992)? Could these properties be more beneficial in designing computers for specific applications, for example artificial intelligence of crypto-mining? How could the application of superconductor materials enhance cryocomputing? The answers to these questions

would help to better understand whether it is necessary to pay extra energy cost for the cryogenic cooling of CMOS electronics.

Another side of the problem is the performance of the cryocooler itself. At present, the knowledge of how to build efficient high-capacity cryocoolers is inadequate. The efficiency of a cryogen-free cryocoolers operated at 4 K is around 10% of the ideal Carnot cryocooler (Strobridge, 1974) and has not improved significantly over the last 50 years (Martin *et al.*, 2021). Many questions related to design, material choice and reliability of these complex thermal machines are still not answered. Furthermore, there is always the question of the coupled operation of the cryocooler and cryoprocessor. Taken together, the answers to these questions would help to reduce the energy cost and might offset it with other benefits.

An important implication of this work is the knowledge to operate cryo-CMOS electronics for quantum computing. Recent work in this area focused on the design and operation of cryoelectronics. However, much is to be learned about modifying the parameters of the cryospace for these types of devices. The operational temperatures currently discussed in the literature are at the level of several kelvins. The present work discusses the operation of electronics in the cryospace with a temperature of 173 K. This is a significant difference and a limitation to generalizing the results to lower temperature ranges. Although the empirical base is limited, the analytical model, at least in theory, is independent of the cryocooler choice and the temperature range (Eq. 19) because it is derived using the thermal-electrical analogy. This relation could be utilized to model cryospaces with different cryocooling technologies described by thermal resistances  $R_c$ ,  $R_{atm-g}$ ,  $R_{gc}$ , and  $R_{s-g}$ , provided that the latter take into account the change of material properties at the temperature level of several kelvins.

### **IV.2** Future work

Two interesting research directions could be pursued based on the results of this work:

- Analytical and experimental analysis of a coupled cryo-CMOS electronics and regenerative cryocooler operated at the temperature of low-temperature heat recovery applications.

- Optimization of design and operational parameters of the cryo-CMOS electronics and cryospaces for their joined operation.

# **V** Conclusions

This work aimed to derive an effective analytical relationship between the junction temperature of the Si-based semiconductor integrated circuit and the known and controllable parameters of the cryospace. We developed a model to predict the steady-state junction temperature of the integrated circuit operated in the cryospace using the thermal-electrical analogy. Our experimental validation demonstrated that the prediction accuracy of the model is  $\pm 2\%$ . Our results showed the increase of possible clock frequencies through cryogenic cooling of a simple CMOS integrated circuit by the factor of 3. Our findings can be applied to analyze the coupling of cryo-CMOS electronics and cryocoolers over a wide range of cryogenic temperatures for the design and control of cryo-CMOS devices.

### References

- Adamatzky, A. (2014) 'Unconventional computing', *International Journal of General Systems*, 43(7), pp.671–672. Available at: <u>https://doi.org/10.1080/03081079.2014.927149</u>.

- Apertet, Y., Ouerdane, H., Michot, A., Goupil, C. and Lecoeur, P. (2013) 'On the efficiency at maximum cooling power', *EPL (Europhysics Letters)*, 103(4), p.40001. Available at: <a href="https://doi.org/10.1209/0295-5075/103/40001">https://doi.org/10.1209/0295-5075/103/40001</a>.

- Carlson, D.M., Sullivan, D.C., Bach, R.E. and Resnick, D.R. (1989.) 'The ETA 10 liquid-nitrogen-cooled supercomputer system,' *IEEE transactions on electron devices*, 36(8), pp.1404-1413. Available at: <u>https://doi.org/10.1109/16.30952</u>.

- Chu, R.C. (1999) 'A review of IBM sponsored research and development projects for computer cooling', *Fifteenth Annual IEEE Semiconductor Thermal Measurement and Management Symposium (Cat. No. 99CH36306)*, pp. 151-165. Available at: <u>https://doi.org/10.1109/STHERM.1999.762443</u>.

- Clark, W.F., El-Kareh, B., Pires, R.G., Titcomb, S.L. and Anderson, R.L. (1992) 'Low temperature CMOS-a brief review', *IEEE Transactions on Components Hybrids and Manufacturing Technology*, 15(3), pp.397-404. Available at: <u>https://doi.org/10.1109/33.148509</u>.

- Dyakonov, M. I. (2020) 'Will we ever have a quantum computer?', *SpringerBriefs in Physics*. Cham: Springer International Publishing. Available at: <u>https://doi.org/10.1007/978-3-030-42019-2</u>.

- Holmes, D.S., Ripple, A.L. and Manheimer, M.A. (2013) 'Energy-efficient superconducting computing— Power budgets and requirements' *IEEE Transactions on Applied Superconductivity*, 23(3), pp.1701610-1701610. Available at: <u>https://doi.org/10.1109/TASC.2013.2244634</u>.

- Giustino, F., Lee, J.H., Trier, F., Bibes, M., Winter, S.M., Valentí, R., Son, Y.W., Taillefer, L., Heil, C., Figueroa, A.I. and Plaçais, B. (2021) 'The 2021 quantum materials roadmap', *Journal of Physics: Materials*, 3(4), p.042006. Available at: <u>https://doi.org/10.1088/2515-7639/abb74e</u>.

- IEA. (2018), 'The future of cooling. Opportunities for energy-efficient air conditioning', *Report*, Paris: International Energy Agency. Available at: <u>https://www.iea.org/reports/the-future-of-cooling</u> (Accessed: 18 July 2021).

- Isaac, R.D. (2000) 'The future of CMOS technology', *IBM Journal of Research and Development*, 44(3), pp.369-378. Available at: <u>https://doi.org/10.1147/rd.443.0369</u>.

- Khan, H.N., Hounshell, D.A. and Fuchs, E.R. (2018) 'Science and research policy at the end of Moore's law', *Nature Electronics*, 1(1), p.14. Available at: <u>https://doi.org/10.1038/s41928-017-0005-9</u>.

- Krane, R. J., Parsons, J. R., & Bar-Cohen, A. (1988) 'Design of a candidate thermal control system for a cryogenically cooled computer', *IEEE Transactions on Components, Hybrids, and Manufacturing Technology*, 11(4), pp. 545–556. Available at: <u>https://doi.org/10.1109/33.16696</u>.

- Kuzmicz, W. (2017) 'The future of CMOS: More Moore or the next big thing?', In 2017 MIXDES-24th International Conference" Mixed Design of Integrated Circuits and Systems, pp. 21-26, IEEE. Available at: <u>https://doi.org/10.23919/MIXDES.2017.8004587</u>.

- Martin, M.J., Hughes, C., Moreno, G., Jones, E.B., Sickinger, D., Narumanchi, S. and Grout, R. (2021) 'Energy use in quantum data centers: Scaling the impact of computer architecture, qubit performance, size, and thermal parameters', *arXiv.org*. Available at: <u>https://arxiv.org/abs/2103.16726v1</u>.

- Otaka, T., Ota, M., Murakami, K. and Sakamoto, M. (2002) 'Study of performance characteristics of a small Stirling refrigerator', *Heat Transfer—Asian Research: Co-sponsored by the Society of Chemical Engineers of Japan and the Heat Transfer Division of ASME*, 31(5), pp. 344-361. Available at: <u>https://doi.org/10.1002/htj.10033</u>.

- Rose, K., Mangaser, R., Mark, C. and Sayre, E. (1999) "Cryogenically cooled CMOS', *Critical reviews in solid state and materials sciences*, 24(1), pp.63-99. Available at: <u>https://doi.org/10.1080/10408439991329170</u>.

- Smirnov, D. and Ouerdane, H. (2021) 'Prediction of temperatures in a cryogenic space cooled by the Stirling cryocooler', *Internation Journal of Refrigeration*, submitted manuscript.

- Smirnov, D., Dvortsov, V., Saichenko, A., Tkachenko, M., Kukolev, M., Bischi, A. and Ouerdane, H. (2019) 'Experimental study of a high-tolerance piston-cylinder pair in the alpha Ross-yoke Stirling refrigerator', *International Journal of Refrigeration*, 100, pp.235-245. Available at: <u>https://doi.org/10.1016/j.ijrefrig.2019.01.018</u>.

- Strobridge, T. R. (1974) 'Cryogenic Refrigerators-An Updated Survey', National Bureau of Standards, technical note 655, pp. 1-12.

- Ungerer, T. and Carpenter, P. (eds.) (2018) 'Eurolab-4-HPC long-term vision on high-performance computing', *Report*, second edition, Foundation for a Centre of Excellence in High-Performance Computing Systems. Available at: <u>https://www.eurolab4hpc.eu/vision/</u> (Accessed: 18 July 2021).

- Amiri, L., Madadian, E., Bahrani, N. and Ghoreishi-Madiseh, S.A. (2021) 'Techno-economic analysis of waste heat utilization in data centers: application of absorption chiller systems. *Energies*, 14(9), p.2433. Available at: <u>https://doi.org/10.3390/en14092433</u>.

- Roser, M. and Ritchie, H. (2013) 'Computing efficiency, 1971 to 2015' in *Technological Progress*. Published online at OurWorldInData.org. Available at: <u>https://ourworldindata.org/technological-progress</u> (Accessed: 26 July 2021).

- Xue, X., Patra, B., van Dijk, J.P., Samkharadze, N., Subramanian, S., Corna, A., Wuetz, B.P., Jeon, C., Sheikh, F., Juarez-Hernandez, E. and Esparza, B.P. (2021) 'CMOS-based cryogenic control of silicon quantum circuits', *Nature*, 593(7858), pp.205-210. Available at: <u>https://doi.org/10.1038/s41586-021-03469-4</u>.

- Pauka, S.J., Das, K., Kalra, R., Moini, A., Yang, Y., Trainer, M., Bousquet, A., Cantaloube, C., Dick, N., Gardner, G.C. and Manfra, M.J. (2021) 'A cryogenic CMOS chip for generating control signals for multiple qubits', *Nature Electronics*, 4(1), pp.64-70. Available at: <u>https://doi.org/10.1038/s41928-020-00528-y</u>.

- Smirnov D.S. (2021) 'Complex flow and thermal physics in regenerative cryocoolers', Thermal Motors LLC, pp. 1-6. Available at: <u>http://dx.doi.org/10.13140/RG.2.2.33237.76005</u>.

# Appendix

Calculation of limits in Table 2.

$\begin{aligned} \text{Case 1}) \ R_{\text{atm-g}} &\to \infty, R_{\text{atm-g}} = x, R_{\text{g-c}} = b : \lim_{x \to \infty} \gamma = 0 \\ \gamma &= \frac{b}{b + x - \frac{x}{b \cdot \text{C} + 1}} = \frac{b}{\frac{b(b \cdot \text{C} + 1) + xb \cdot \text{C} + x - x}{b \cdot \text{C} + 1}} = \frac{b \cdot \text{C} + 1}{x \cdot \text{C} + b \cdot \text{C} + 1} \Rightarrow \lim_{x \to \infty} \gamma = 0 \\ R_{\text{atm-g}} \gamma &= \frac{x(b \cdot \text{C} + 1)}{x \cdot \text{C} + b \cdot \text{C} + 1} = \frac{b \cdot \text{C} + 1}{\frac{b \cdot \text{C} + 1}{x} + \text{C}} \Rightarrow \lim_{R_{\text{atm-g}} \to \infty} R_{\text{atm-g}} \gamma = b + \frac{1}{C}. \end{aligned}$

Case 3)

$$R_{g-c} \rightarrow \infty$$

,  $R_{g-c} = x$ ,  $R_{atm-g} = a : \lim_{x \to \infty} \gamma = 1$

$$\gamma = \frac{x}{a+x-\frac{a}{x\cdot C+1}} = \frac{x}{\frac{x\cdot a\cdot C+a+x(x\cdot C+1)-a}{x\cdot C+1}} = \frac{x\cdot C+1}{a\cdot C+(x\cdot C+1)} = \frac{1}{\frac{a\cdot C}{x\cdot C+1}+1} \Longrightarrow \lim_{x\to\infty} \gamma = 1.$$

Case 4)

$$R_{g-c} \to 0, R_{g-c} = x, R_{atm-g} = a : \lim_{x \to 0} \gamma = \frac{1}{a \cdot C + 1}$$

$$\gamma = \left[ \text{from} \left( 3 \right) \right] = \frac{1}{\frac{a \cdot C}{x \cdot C + 1} + 1} \Longrightarrow \lim_{x \to 0} \gamma = \frac{1}{a \cdot C + 1}$$

$$\begin{split} T_{j} &= q_{s} \left( R_{j\cdot s} + R_{s\cdot g} + \gamma \cdot R_{atm-g} \right) + \gamma \cdot T_{atm} = q_{s} \left( R_{j\cdot s} + R_{s\cdot g} + \frac{R_{atm-g}}{R_{atm-g} \cdot C + 1} \right) + \gamma \cdot T_{atm} = \\ &= q_{s} \left( R_{j\cdot s} + R_{s\cdot g} + \frac{1}{C + \frac{1}{R_{atm-g}}} \right) + \frac{T_{atm}}{R_{atm-g} \cdot C + 1} = q_{s} \left( R_{j\cdot s} + R_{s\cdot g} + \frac{R_{c} \cdot R_{atm-g}}{R_{c} + R_{atm-g}} \right) + \frac{R_{c} \cdot T_{atm}}{R_{c} + R_{atm-g}} \end{split}$$